# LAP VIDEO PROCESSING CORE

Before

# **Automatic Contrast** *Enhancement* **Solution**

- High Quality

- Low Cost

- Low Power

## **OVERVIEW**

The Local Area Processing (LAP) Core utilizes adaptive area contrast enhancement techniques to adaptively provide a high level (yet configurable) amount of detail for a wide variety of video/camera sources.

#### **DYNAMIC**

Best suited for high dynamic range IR or visible applications, and performs well in other situations.

#### **FOCUSED**

Take advantage of a proprietary filtering technique that handles high complexity and prevents processed image artifacts.

#### **VERSATILE**

Optimize the algorithm for your custom application via programmable parameters.

#### **CLARIFIED**

Make details visible in under-exposed or over-exposed portions of the image with low dynamic range IR, traditional CCD, or CMOS imagers.

#### **SCALABLE**

Leverage the filtering kernel, which scales well with larger source images and eliminates the halo artifacts normally created by other methods.

# **IMAGE QUALITY**

- Dynamic pixel by pixel area based contrasting with programmable window size

- Reduced blurring edges

- Free of halo artifacts

- Superior to histogram equalization or other conventional techniques

- See into shadows. Maximal contrast in darks and in lights, simultaneously

# **APPLICATIONS**

- Uncooled or cooled IR/FLIR systems

- CCD sensor based imaging systems

- CMOS sensor based imaging systems

#### **IMPLEMENTATION**

- Small, easy to configure parameter set

- Programmable limits to auto-adaptive local area window sizing

- No frame delay

- Ability to fine tune the algorithm for a wide variety of video input conditions

- Requires relatively small number of resources (low power and system cost)

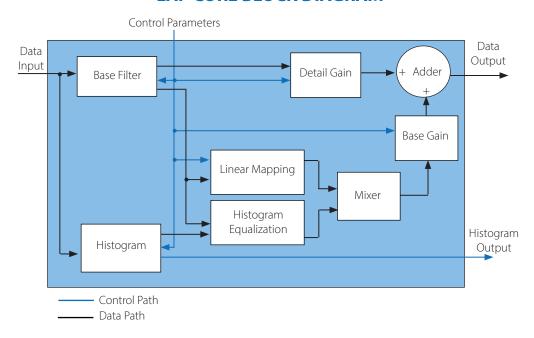

## LAP CORE BLOCK DIAGRAM

#### **RESOURCE UTILIZATION**

The LAP Video Processing Core is not limited to any vendor specific implementation. Versions are available for major FPGA vendors and can be created for any custom ASIC application. The following table shows resource requirements as implemented in a Xilinx device.

| MODULE      | LUTs | FFs  | MULTIPLIERS | 18k x 1 BLOCK<br>RAMs |

|-------------|------|------|-------------|-----------------------|

| 10-BIT B&W  | 1221 | 1386 | 8           | 3                     |

| 14-BIT B&W  | 1385 | 2140 | 9           | 4                     |

| 8-BIT Color | 1796 | 2188 | 10          | 3                     |

# **UNPROCESSED VS. LAP PROCESSED**